### **Features and Benefits**

- Synchronous rectification for low power dissipation

- Drives four N-channel MOSFETs

- Internal UVLO and thermal shutdown circuitry

- Hall element input

- PWM current limiting

- Dead time protection

- FG output

- RD output

- Lock detect protection

- High V<sub>BB</sub> absolute maximum

- Soft start

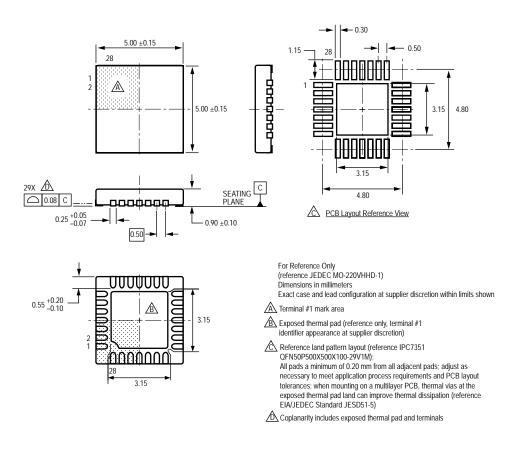

# Package: 28-pin QFN with exposed thermal pad (suffix ET)

### Description

Designed for pulse width modulated (PWM) current control of single phase brushless fans, the A4930 minimizes external component count and integrates all the key features required for high-current fans. Internal synchronous rectification control circuitry is provided to improve power dissipation in the external MOSFETs during PWM operation. Internal circuit protection includes thermal shutdown with hysteresis, rotor lock, and dead time protection.

The A4930 is supplied in a 0.90 nominal overall height,  $5 \text{ mm} \times 5 \text{ mm}$ , 28-pin QFN with exposed thermal pad, (suffix ET). It is lead (Pb) free with 100% matte tin leadframe plating.

#### Selection Guide

| Part Number  | Packing                    |  |  |

|--------------|----------------------------|--|--|

| A4930METTR-T | 1500 pieces per 7-in. reel |  |  |

#### **Absolute Maximum Ratings**

| Characteristic              | Symbol               | Notes   | Rating     | Units |

|-----------------------------|----------------------|---------|------------|-------|

| Load Supply Voltage         | V <sub>BB</sub>      |         | 36         | V     |

| Hall Input                  | V <sub>Hx</sub>      |         | –0.3 to 6  | V     |

| Logic Input Voltage Range   | V <sub>IN</sub>      |         | –0.3 to 6  | V     |

| Operating Temperature Range | T <sub>A</sub>       | Range M | -20 to 105 | °C    |

| Junction Temperature        | T <sub>J</sub> (max) |         | 150        | °C    |

| Storage Temperature Range   | T <sub>stg</sub>     |         | -40 to 150 | °C    |

#### THERMAL CHARACTERISTICS may require derating at maximum conditions

| Characteristic                              | Symbol | Test Conditions*                    | Value | Units |

|---------------------------------------------|--------|-------------------------------------|-------|-------|

| Package Thermal Resistance R <sub>0JA</sub> |        | 4-layer PCB based on JEDEC standard | 32    | °C/W  |

\*Additional thermal information available on Allegro website.

### ELECTRICAL CHARACTERISTICS<sup>1</sup> valid at $T_A = 25$ °C, $V_{BB} = 12$ V, unless noted otherwise

| Characteristic                                            | Symbol               | Test Conditions                                        | Min. | Typ. <sup>2</sup> | Max. | Units |

|-----------------------------------------------------------|----------------------|--------------------------------------------------------|------|-------------------|------|-------|

| Load Supply Voltage Range                                 | V <sub>BB</sub>      | Operating                                              | 8    | 12                | 36   | V     |

| Motor Supply Current I <sub>BB</sub> f <sub>PWM</sub> < 3 |                      | f <sub>PWM</sub> < 30 kHz, C <sub>load</sub> = 1000 pf | _    | 5                 | 7    | mA    |

| VREG5                                                     | V <sub>5</sub>       | I <sub>load</sub> = 10 mA                              | 4.7  | 5                 | 5.3  | V     |

| VREG5 Current Limit                                       | I <sub>REG5</sub>    |                                                        | 15   | -                 | _    | mA    |

| VREG5 Load Regulation                                     | V <sub>REG5</sub>    | I <sub>REG5</sub> = 1 to 10 mA                         | _    | 12                | 30   | mV    |

| Control Logic                                             |                      |                                                        |      | •                 |      |       |

|                                                           | V <sub>IN(1)</sub>   |                                                        | 2    | -                 | _    | V     |

| Logic Input Voltage                                       | V <sub>IN(0)</sub>   |                                                        | _    | -                 | 0.8  | V     |

| PWM Pin Input Current                                     | I <sub>IN(0)</sub>   | V <sub>IN</sub> = 0, 50 kΩ pull-up                     | _    | -100              | -    | μA    |

| Other Logic Pin Input Current                             | I <sub>IN(1)</sub>   | V <sub>IN</sub> = 3.3                                  | _    | -34               | -    | μA    |

| Gate Drive                                                |                      |                                                        | I.   | •                 |      |       |

| High Side Gate Drive Output                               | V <sub>GHx</sub>     | Relative to V <sub>BB</sub> , VBB = 12 V               | 7    | -                 | _    | V     |

| Low Side Gate Drive Output                                | V <sub>GLx</sub>     |                                                        | 7    | _                 | 8.5  | V     |

| Gate Drive Current Turn-on                                | Ι <sub>G</sub>       | GHx = GLx = 4 V                                        | _    | 20                | _    | mA    |

| Gate Drive Pulldown                                       | R <sub>DS</sub>      |                                                        | _    | 40                | -    | Ω     |

| Dead Time                                                 | t <sub>DEAD</sub>    |                                                        | 700  | 1000              | 1300 | ns    |

| Control                                                   | ·                    |                                                        | L.   |                   |      |       |

| Soft Start Time                                           | t <sub>ss</sub>      | C <sub>LD</sub> = 0.47 μF                              | -    | 300               | _    | ms    |

| Internal PWM Frequency                                    | f <sub>PWM</sub>     | C <sub>PWM</sub> = 470 pF                              | 15   | 21                | 27   | kHz   |

| CPWM Output Voltage                                       | V <sub>PP</sub>      | C <sub>PWM</sub> = 470 pF                              | _    | 2                 | _    | V     |

| CPWM Low Threshold                                        | V <sub>LO</sub>      |                                                        | _    | 1.5               | _    | V     |

| CPWM High Threshold                                       | V <sub>HI</sub>      |                                                        | _    | 3.5               | -    | V     |

| SIN Input Impedance                                       | Z <sub>IN</sub>      |                                                        | _    | 200               | -    | kΩ    |

| Protection                                                | L                    | •                                                      | ŀ    | •                 | •    |       |

| Thermal Shutdown Temperature                              | T <sub>JTSD</sub>    |                                                        | _    | 165               | _    | °C    |

| Thermal Shutdown Hysteresis                               | T <sub>JTSDhys</sub> |                                                        | _    | 15                | _    | °C    |

Continued on the next page...

#### ELECTRICAL CHARACTERISTICS<sup>1</sup> valid at $T_A = 25$ °C, $V_{BB} = 12$ V, unless noted otherwise

| Characteristic                            | Symbol               | Test Conditions                        | Min. | Typ. <sup>2</sup> | Max. | Units |

|-------------------------------------------|----------------------|----------------------------------------|------|-------------------|------|-------|

| VBB Undervoltage Lockout Enable Threshold | V <sub>BBUV</sub>    | Rising V <sub>BB</sub>                 | _    | 7.5               | 7.85 | V     |

| VBB Undervoltage Lockout Hysteresis       | V <sub>BBUVhys</sub> |                                        | 0.3  | 0.8               | Ι    | V     |

| VCP Undervoltage Lockout Enable Threshold | V <sub>CPUV</sub>    | Relative to $V_{BB}$ , $V_{BB}$ rising | _    | 5.4               | Ι    | V     |

| Lock Detect On-Time                       | t <sub>LDon</sub>    | C <sub>LD</sub> = 0.1 μF               | -    | 1                 | Ι    | s     |

| Lock Detect Off-Time                      | t <sub>LDoff</sub>   | C <sub>LD</sub> = 0.1 μF               | -    | 15                | -    | s     |

| Hall Logic                                |                      |                                        |      |                   |      |       |

| Hall Input Current                        | I <sub>HALL</sub>    | V <sub>IN</sub> = 1.2 V                | -1   | 0                 | 1    | μA    |

| Common Mode Input Range                   | V <sub>CMR</sub>     |                                        | 0.2  | -                 | 3    | V     |

| AC Input Voltage Range                    | V <sub>HALL</sub>    |                                        | 60   | -                 | Ι    | mVp-p |

| Hall Threshold                            | V <sub>th</sub>      | Difference in Halls at FG transition   | _    | 10                | Ι    | mV    |

| Hysteresis Width                          | V <sub>HYS</sub>     |                                        | 5    | 20                | 35   | mV    |

| Pulse Reject Filter                       | V <sub>PU</sub>      |                                        | -    | 50                | Ι    | mv    |

| Commutation Delay                         | t <sub>CD</sub>      | R <sub>CDEL</sub> = 50 kΩ              | 1    | 2                 | 3    | μs    |

| FG and RD Outputs                         |                      |                                        |      |                   |      |       |

| Output Saturation Voltage                 | V <sub>OL</sub>      | I = 2 mA                               | -    | 0.27              | 0.4  | V     |

| Leakage Current                           | V <sub>OH</sub>      | V = 5 V                                | _    | -                 | 1    | μA    |

<sup>1</sup>For input and output current specifications, negative current is defined as coming out of (sourcing) the specified device pin.

<sup>2</sup>Typical data are for initial design estimations only, and assume optimum manufacturing and application conditions. Performance may vary for individual units, within the specified maximum and minimum limits.

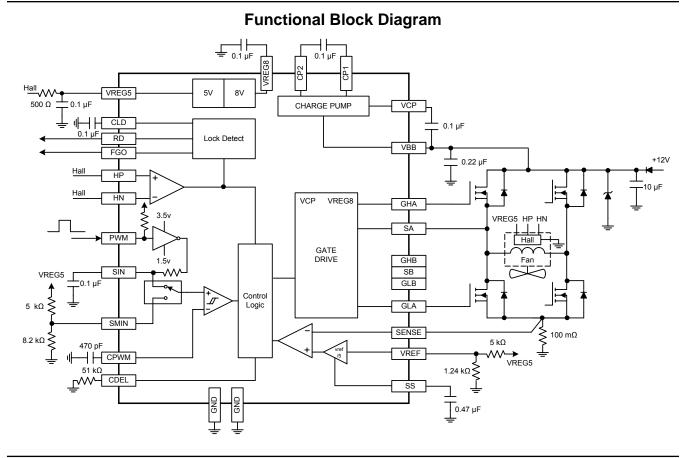

### **Functional Description**

**VREG5** This pin should be decoupled with a 0.1  $\mu$ F capacitor to ground. VREG5 can supply up to 15 mA, which can used to power the external Hall element.

**VREG8** This pin should be decoupled with a 0.1  $\mu$ F capacitor to ground. VREG8 is used to power the low-side gate drive circuits.

**Charge Pump** The charge pump is used to generate a supply above  $V_{BB}$  to drive the high-side MOSFETs. The VCP voltage is internally monitored, and in the case of a fault condition, the outputs of the device are disabled.

**Lock Detect** The IC detects a locked rotor condition by checking to ensure that the FG output signal is continuously changing. The length of time allowed for a stoppage before evaluating a locked condition,  $t_{LD}$ , is set by capacitor connected to CLD pin.  $C_{LD}$  produces a triangle waveform with a frequency that is linearly related to the capacitor value. The definition of  $t_{LD}$  is defined as 8 cycles of this triangle waveform, and its value can be calculated as:

$$t_{\rm LD} = C_{\rm LD} \times (10 \text{ s} / \mu \text{F})$$

. (1)

If an FG transition is not detected within  $t_{LD}$ , the IC will disable the appropriate source driver and hold both sink drivers on. The circuit will automatically retry with a 15:1 ratio of off-time to ontime. An RD pin logic high indicates this fault condition.

**Current Limit and Soft Start** To minimize demand on the power supply, peak current is controlled. Initially, with the fan at a stand-still, the turn-on of the bridge results in current rising according to the L/R time constant of the motor. To prevent overstress, this peak current is regulated by an internal PWM control circuit. When the outputs of the full-bridge are turned on, current increases in the motor winding until it reaches a value given by:

$$I_{\text{TRIP}} = V_{\text{REF}} / 5 \times R_{\text{SENSE}} \quad . \tag{2}$$

The  $R_{SENSE}$  value should be chosen to keep the peak sense voltage within the range of 200 to 500 mV, according to the relationship:

$$R_{\rm SENSE} < 500 \text{ mV} / I_{\rm TRIP} \tag{3}$$

At the trip point, the sense comparator resets the source enable latch, turning off the source driver. At this point, load inductance causes the current to recirculate for 50  $\mu$ s.

A soft start capacitor, CSS, can be connected to the SS pin to set the rate for slowly ramping-up the load current to the maximum value, according to the relationship:

$$t_{\rm SS} = (C_{\rm SS} \times V_{\rm REF}) / 3.3 \text{E-6}$$

(4)

In this case the current limit will likely not be achieved and there will be less demand on the input power supply. If this feature is not utilized, the SS pin should be left open.

**Synchronous Rectification** When a PWM off-cycle is triggered, load current recirculates. The A4930 synchronous rectification feature turns on the appropriate MOSFETs during current decay, and effectively shorts out the body diodes of the low  $R_{DS(on)}$  driver.

**TSD** If the die temperature exceeds approximately  $165^{\circ}$ C, the outputs will be disabled until the internal temperature falls below a hysteresis level of  $15^{\circ}$ C.

**Shutdown** In the event of a fault due to excessive junction temperature, or low voltage on VCP or VBB, the outputs of the device are disabled until the fault condition is removed. At power-up the UVLO circuit disables the drivers until the UVLO threshold is reached.

**CPWM** This capacitor sets the frequency of the internal PWM circuit. The value is typically from 15 to 30 kHz.

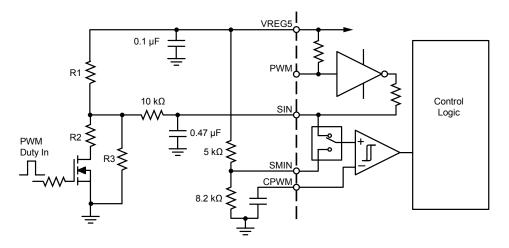

**PWM** The IC accepts a direct input PWM signal with a level in the range from 0 to 6 V. The duty cycle, DC, of the input to this pin is converted to an analog voltage that is output on the SIN terminal as follows:

$$V_{\rm SIN} = 3.5 \text{ V} - 2 \times \text{DC} \quad . \tag{5}$$

If the PWM input is not used, then leave this pin open circuit. Direct external PWM control can be utilized by applying the signal to the SIN input (refer to the Applications Information section). This can be implemented to create different PWM input to PWM output transfer functions.

## A4930

**SIN** An analog voltage input to this pin sets the duty cycle applied to the fan winding. For temperature-based systems, connect SIN to a thermistor output. For systems with direct input to the PWM pin, the pin should be decoupled with a 0.1  $\mu$ F capacitor. If variable fan speed is not required, for 100% duty cycle, connect this pin to GND. The input impedance is 200 k $\Omega$  (referenced to a 3.5 or 1.5 V rail).

**SMIN** An analog voltage input to this pin sets the minimum speed duty cycle to the fan winding. The PWM comparator chooses either SIN or SMIN to determine the output duty cycle, which-

ever is set to a lower voltage. For 100% duty cycle applications, connect this pin to GND.

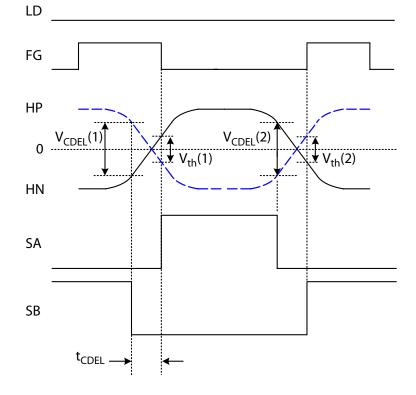

**CDEL** A resistor connected between this pin and GND sets the level at which the A4930 switches to slow decay mode in advance of the Hall zero crossing as shown here:

$V_{\text{CDEL}} = (2950 / R_{\text{CDEL}}) - 7 \text{ mV}$  (mV) (6)

The resistor should be 25 to 100 k $\Omega$ . If this feature is not used, the CDEL pin should be pulled up to  $V_{REG5}$  with a 5 k $\Omega$  resistor.

$$\begin{split} &V_{th}(1) = V_{HP} - V_{HN} = 10 \text{ mV (Typical)} \\ &V_{th}(2) = V_{HN} - V_{HP} = 10 \text{ mV (Typical)} \\ &V_{HYS} = V_{th}(1) + V_{th}(2) = 20 \text{ mV (Typical)} \end{split}$$

### **Applications Information**

**Overvoltage** In a typical fan application, there is a blocking diode that prevents currents from flowing back out of the fan assembly to the 12 V supply. When the fan commutates before the current has decayed to zero, the current charges up the VBB bypass capacitor.

The larger the bypass capacitor, the less the voltage overshoot. Typically, a clamp diode is required to dissipate energy from the inductive kickback to avoid exceeding the maximum rating for  $V_{\rm BB}$ , 36 V.

**Layout** Small form factor PCBs present a layout challenge for the application. The layout would be restricted by the placement of the Hall element, the location of the motor connectors, and the common requirement that all components be placed on one side of the PCB. For optimum results, consider the following recommendations:

Place the external MOSFET bridge close to the power connector. The bridge includes two dual N-channel MOSFETs, a sense resistor, and a power supply capacitor. This will keep the large current flows in one area of the PCB and avoid ground loop problems.

- Keep the sense connection to the power bridge as short as possible. This can be achieved by positioning the MOSFETs next to each other, and by connecting the source of the sink side MOS-FETs via a short trace, preferably on the surface of the PCB, under the MOSFETs. A short trace here would minimize voltage spikes due to inductance in the path, where currents switch at high di/dt.

- Place the power traces from the MOSFETs to the motor connector on the opposite side of the PCB. If possible, on that side isolate the power traces by ground traces in order to minimize interference with other signal traces due to the high dv/dt of the power traces.

- Locate the A4930 to minimize the length of the GHx/GLx/Sx traces to the power stage.

- Connect the GND pins of the A4930 to the exposed pad. Use vias under the IC case to connect the exposed pad to the ground plane on the opposite face of the PCB.

**External PWM** Refering to the figure below, if external PWM control is being used, the high voltage level is set by R1, R2, and R3. The low voltage level is set by R1 and R3.

PWM control using External PWM input

7

VCP CP2 CP1 GND GHA NC VBB (27 (26 (26 (25 (23 (23) (23) (22) 28 VREG5 1) (21 SA GHB CLD 2) (20 FG 3) (19 SB PAD (18 VREG8 RD 4) ΗP 5) (17 GLA <u>6</u>) (16 GLB ΗN (15 CDEL  $(\overline{7})$ SENSE PWM 8 CPWM 9 SIN 10 SMIN 11 SS 12 VREF 13 VREF 13

Pin-out Diagram

#### **Terminal List**

| Number | Name  | Description                                             | Number | Name  | Description                                    |

|--------|-------|---------------------------------------------------------|--------|-------|------------------------------------------------|

| 1      | VREG5 | Regulator decoupling terminal                           | 16     | GLB   | Low-side drive for external N-channel MOSFET   |

| 2      | CLD   | Capacitor to set Lock Detect Time                       | 17     | GLA   | Low-side drive for external N-channel MOSFET   |

| 3      | FG    | FG output, fan speed indicator (open drain)             | 18     | VREG8 | Gate drive supply                              |

| 4      | RD    | RD output, high for locked rotor condition (open drain) | 19     | SB    | High-side source connection                    |

| 5      | HP    | Hall input positive                                     | 20     | GHB   | High-side drive for external N-channel MOSFET  |

| 6      | HN    | Hall input negative                                     | 21     | SA    | High-side source connection                    |

| 7      | CDEL  | Commutation delay                                       | 22     | GHA   | High-side drive for external N-channel MOSFET  |

| 8      | PWM   | PWM input                                               | 23     | GND   | Ground                                         |

| 9      | CPWM  | Capacitor to set internal frequency                     | 24     | CP1   | Charge pump capacitor terminal                 |

| 10     | SIN   | Speed analog input/adjusted PWM output                  | 25     | CP2   | Charge pump capacitor terminal                 |

| 11     | SMIN  | Minimum speed analog input                              | 26     | VCP   | Reservoir capacitor terminal                   |

| 12     | SS    | Connection for soft start capacitor                     | 27     | VBB   | Supply voltage                                 |

| 13     | VREF  | Current limit setpoint                                  | 28     | NC    | Not connected                                  |

| 14     | GND   | Ground                                                  |        |       | Thermal pad, connect to GND plane with vias to |

| 15     | SENSE | Sense resistor connection                               | – Pad  |       | bottom of PCB                                  |

### Package ET 28-Pin QFN with Exposed Thermal Pad

Copyright ©2008, Allegro MicroSystems, Inc.

The products described here are manufactured under one or more U.S. patents or U.S. patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com